运行VLC 媒体播放器( 或者类似的) 的主机PC 用于查看IP 监视摄像机参考设计的流视频输出。如图7 所示,主机和EP3C120 开发套件之间需要的唯一链接是以太网电缆。

IP 监视摄像机参考设计的性能指标包括速度、延时、功耗和资源利用率。

在Cyclone III EP3C120I7 开发板上实现参考设计时,DDR 时钟频率为150 MHz,足以使用H.264 基线类或者主要类来压缩720p30 视频帧。Avalon-MM 总线架构运行在75MHz,H.264 编码器内核运行在150 MHz。DDR2 存储器控制器、Avalon-MM 总线架构以及H.264 内核通过同步半速率桥接进行连接,以减小时钟域之间的延时。Nios II 处理器和TSE 的时钟为125 MHz。采用了Nios II/F( 快速) 版的Nios II 处理器,具有8-Kbyte 指令高速缓存、8-Kbyte 数据高速缓存,并且支持浮点。

从传感器输入到ISP,直至H.264 编码器输出的延时小于两帧,它主要来自图像数据的双缓冲。在对以前的帧进行编码时总是将新输入帧写入存储器。

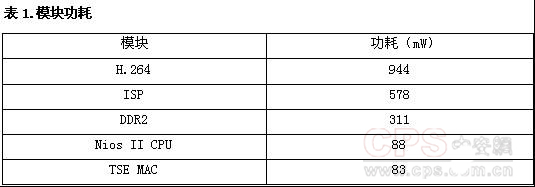

参考设计总功耗包括所有的辅助模块和I/O 的功耗,达到2.7 W。表1 显示了参考设计中使用的每一主要模块的功耗。其余的700mW 来自Avalon 总线架构、颜色空间转换和参考设计的I/O 附件。

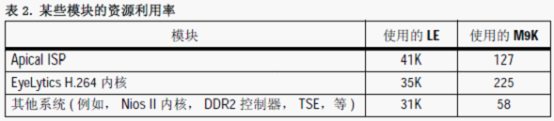

在Cyclone EP3C120 中实现整个参考设计时,其资源利用率为:

■ 107K 逻辑单元(LE) (90% 器件利用率)■ 410 M9K 嵌入式存储器(95% 器件利用率)■ 140 个嵌入式乘法器9 位单元(24% 器件利用率)

表2 列出了某些模块的资源利用率。

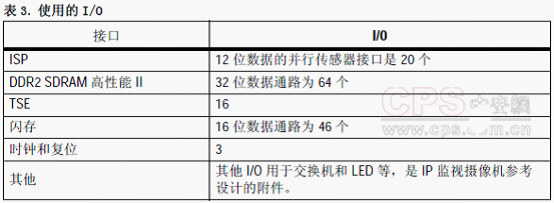

表3 列出了使用的I/O。

基于FPGA 的体系结构非常灵活,可以进行定制,完全能够在大家都了解的标准硬件平台上实现。通过这种灵活性,可以增强和修改系统体系结构,以适应不同的系统需求。由于采用了标准HDL 来实现设计,因此,很容易提高摄像机分辨率,增加定制视频处理功能或者视频分析引擎。而且,还可以通过以太网进行远程更新。例如,把新的FPGA 编程文件发送至Nios II 嵌入式处理器,然后将文件写入闪存,从而重新配置系统或者改变传感器和ISP 设置。在单片FPGA 中集成整个IP 监视摄像机参考设计减少了芯片数量,节省了PCB 空间。不需要与外部器件进行通信,从而减少了I/O 链接,降低了动态功耗,解决了散热问题。针对个性化需求,使用不同的FPGA 图像( 例如,分辨率、帧速率和压缩选项),在一个系统设计中便能够支持多种个性化摄像机。通过纵向移植,可以在同一封装中使用不同逻辑密度的器件。而且,设计可以在任意FPGA 上实现,采用开放设计方案使设计人员能够针对最新的FPGA 进行设计,有了更新的FPGA 系列后,可以进一步提高性能,降低成本和功耗。

Altera 的Cyclone III 和Cyclone IV 系列低成本FPGA 解决了目前最新IP 监视系统设计人员所面临的难题。通过IP 监视摄像机参考设计,Altera 及其合作伙伴提供了从图像采集到IP 包封的全面解决方案,使用集成在Altera SOPC Builder 工具中的系列MegaCore 功能来提供灵活的解决方案,促使产品及时面市。

【中安网原创稿件声明】转载中安网文章时应遵循以下三个规则:1、保持原创文章中图表、图片、音视频的完整性;2、完整标注文章作者[文章前后有说明];3、转载中安网原创中部分内容也要完整标注来源"中安网",违者本网将依法追究。

【想第一时间了解安防行业的重磅新闻吗?请立即关注中安网官方微信(微信号:cpscomcn)——安防行业第一人气微信,万千精彩,千万不要错过!!!

网友评论

共有0条评论 点击查看全部>>24小时阅读排行

本周阅读排行