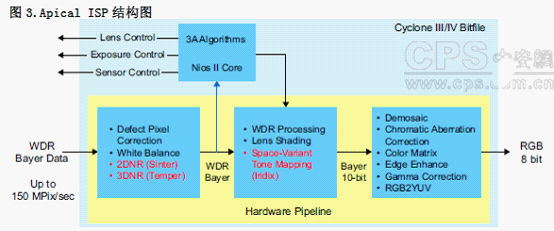

Aptina MT9M033 是0.33" 720p60 WDR CMOS 传感器,主要用于监视摄像机市场。传感器和镜头组合安装在“顶板”上,通过I/O 转换板将其连接至Cyclone III EP3C120开发板。图像传感器流水线CMOS WDR 传感器没有片内图像流水线处理功能,以RAW/Bayer 格式输出图像数据,每像素为20 比特。可以采用下式来计算传感器输出的大量原始数据:20 比特/ 像素 x (1280 x 720) 像素/ 帧x 60 帧/s = >1 Gbit/s由于数据量过大,因此,很难将新一代WDR 传感器连接至监视解决方案中经常使用的ASSP。因此,FPGA 是高效处理数据的理想选择。Apical 的ISP ( 图3) 包括以下功能:

■ 去除热点像素,抑制噪声( 提供空间和时域IP 内核)。

■ 使用Apical 获奖的专利Iridix IP 内核实现单位像素高级色调映射功能

■ 高级去马赛克和颜色校正

与图4 顶部未处理的图像相比,图4 底部显示了Iridix 内核怎样从强对比度场景中尽可能多的提取出细节内容。特别是,较暗的区域并没有受到较亮区域过渡感光的影响。图4.Apical ISP 强对比度场景效应

ISP 输出可以作为参考设计的一个选项,通过Bitec DVI 输出电路板连接至CycloneEP3C120 开发板的第二个HSMC 连接器( 显示在图2 的左侧硬件中)。

【中安网原创稿件声明】转载中安网文章时应遵循以下三个规则:1、保持原创文章中图表、图片、音视频的完整性;2、完整标注文章作者[文章前后有说明];3、转载中安网原创中部分内容也要完整标注来源"中安网",违者本网将依法追究。

【想第一时间了解安防行业的重磅新闻吗?请立即关注中安网官方微信(微信号:cpscomcn)——安防行业第一人气微信,万千精彩,千万不要错过!!!

网友评论

共有0条评论 点击查看全部>>24小时阅读排行

本周阅读排行