目前的视频监视市场在发展过程中遇到了很多要解决的难题,包括从模拟到数字摄像机的过渡、转换到高清(HD) 视频、应用宽动态范围(WDR) 传感器,以及实现进行数据传输和控制的互联网协议(IP) 链接等。针对这些问题,本文介绍了如何采用FPGA构建IP 监视摄像机的参考设计,展示了怎样采用低成本Altera Cyclone III FPGA 构建完整的系统。

在视频监视市场领域,对更高质量视频、高分辨率以及灵活性和功能的需求促进了从模拟到数字摄像机的过渡。在定义上,高清(HD) 视频必须是数字的,因此,采用HD标准也就意味着过渡到数字传感器。HD 视频标准支持更高的帧速率和分辨率,需要H.264 等新压缩方法,促使摄像机具有更强的处理能力。

在各种照明条件( 强光和暗光、强对比度) 下都要求能够提取出所有图像内容,因此,数字摄像机采用了新一类WDR 传感器,摄像机也要求在数字域中实现动态范围压缩。摄像机中数字数据通路的另一优点是可以在摄像机内部进行“分析”处理。

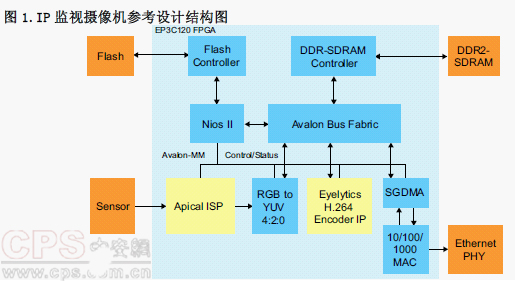

图1 所示为IP 监视摄像机参考设计的顶层结构图和硬件,它主要面向新一代HD (>1MP) WDR 传感器。IP 监视摄像机参考设计结合了Altera 以及多家合作伙伴的硬件和软件知识产权。图1.IP 监视摄像机参考设计结构图

图2 显示了参考设计的硬件平台,基于Cyclone III EP3C120 开发板。Aptina WDR 传感器像素数据被送入Apical 的图像传感器流水线(ISP)。输出数据是YUV4:2:0 格式,写入到外部DDR2 SDRAM 的帧缓冲中,它使用了Altera 视频和图像处理(VIP) 套装提供的组件。然后,使用EyeLytics 提供的内核,以H.264 格式对视频数据进行编码,支持( 在这一应用中)3 级基线/ 主要类视频流,通过以太网在远程主机上观看。散射收集直接存储器访问(SGDMA) 控制器支持Altera 三速以太网(TSE) MegaCore ?功能,将编码后的视频流通过以太网传送到远程客户端。图2.IP 监视摄像机参考设计硬件

【中安网原创稿件声明】转载中安网文章时应遵循以下三个规则:1、保持原创文章中图表、图片、音视频的完整性;2、完整标注文章作者[文章前后有说明];3、转载中安网原创中部分内容也要完整标注来源"中安网",违者本网将依法追究。

【想第一时间了解安防行业的重磅新闻吗?请立即关注中安网官方微信(微信号:cpscomcn)——安防行业第一人气微信,万千精彩,千万不要错过!!!

网友评论

共有0条评论 点击查看全部>>24小时阅读排行

本周阅读排行